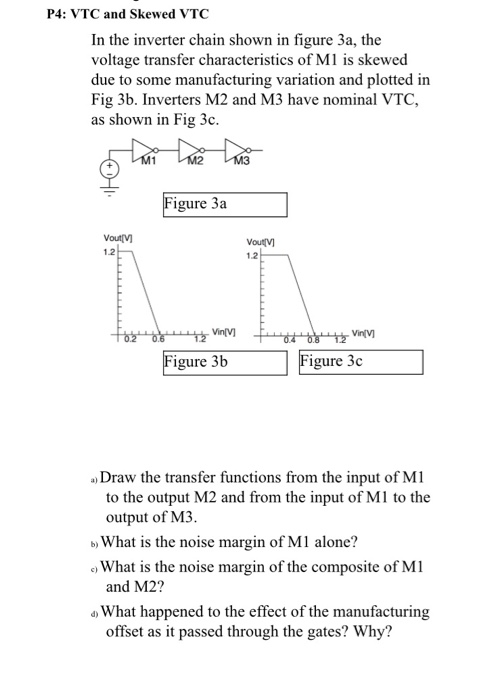

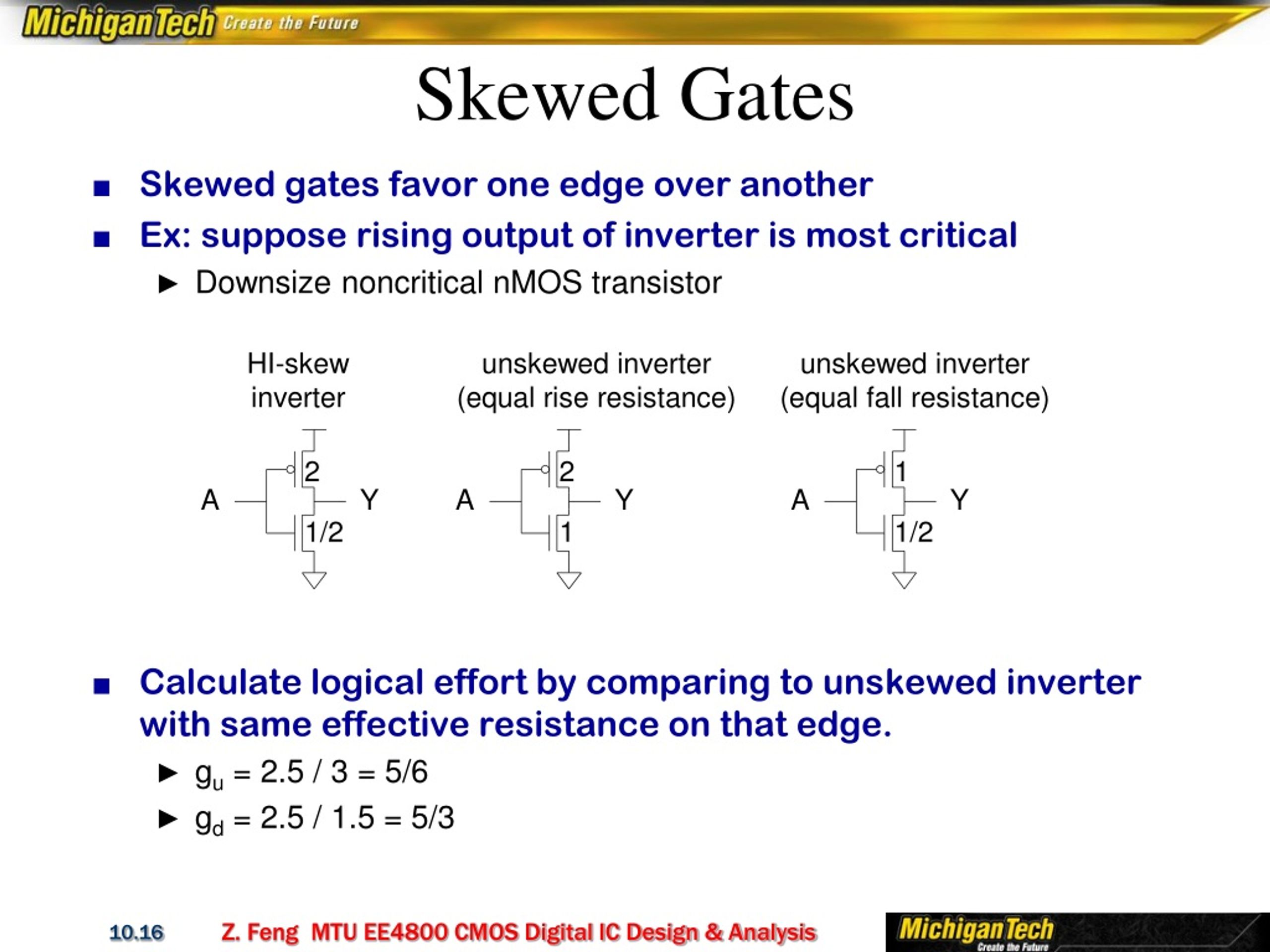

Solved] Design (find the size of NMOS and PMOS transistors) a skewed CMOS inverter that has a rising-edge logical effort (gu) four times smaller tha... | Course Hero

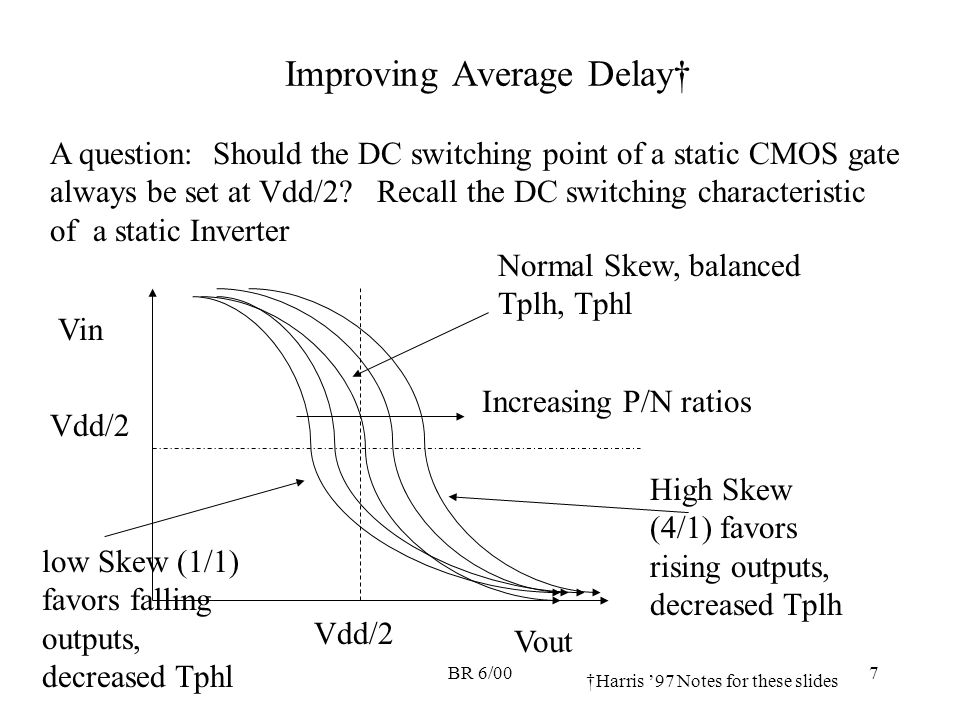

1 Final Exam Review. 2 word7 is high if A2 A1 A0 = 111 word0 is high if A2 A1 A0 = 000 logical effort of each input is (1+3.5)/3 per wordline output. - ppt download

![a) 8T bit-cell [59] (b) Use of "gated skewed inverters" in the design... | Download Scientific Diagram a) 8T bit-cell [59] (b) Use of "gated skewed inverters" in the design... | Download Scientific Diagram](https://www.researchgate.net/profile/Sparsh-Mittal-2/publication/351344022/figure/fig4/AS:1019968816697347@1620190924750/a-8T-bit-cell-59-b-Use-of-gated-skewed-inverters-in-the-design-of-Agrawal-et-al.png)

a) 8T bit-cell [59] (b) Use of "gated skewed inverters" in the design... | Download Scientific Diagram